DOI: 10.3969/j.issn.1009-6868.2017.05.002 网络出版地址; http://kns.cnki.net/kcms/detail/34.1228.TN.20170908.1112.002.html

# 硅光子芯片工艺与设计的发展与挑战

# The Progress and Challenges of Silicon Photonics Process and Design

郭进/GUO Jin 冯俊波/FENG Junbo 曹国威/CAO Guowei

(中国电子科技集团公司第三十八研究所, 安徽 合肥 230088) (CETC38, Hefei 230088, China)

**在** 光子集成技术,是以硅和硅基 村底材料(如 SiGe/Si、SOI等)作 为光学介质,通过互补金属氧化物半 导体(CMOS)兼容的集成电路工艺制 造相应的光子器件和光电器件(包括 硅基发光器件、调制器、探测器、光波 导器件等),并利用这些器件对光子 进行发射、传输、检测和处理,以实现 其在光通信、光互连、光计算等领域 中的实际应用。硅光子技术结合了 以微电子为代表的集成电路技术的 超大规模、超高精度的特性和光子技 术超高速率、超低功耗的优势。在过 去几十年里,作为现代集成电路产业 基石的CMOS工艺取得了令人瞩目的 发展。

而硅光子集成技术作为依存在 CMOS工艺之上的一个新兴技术方 向,从设计方法、设计工具和流程、基 于工艺平台的协同设计等方面很大 程度上参考和借鉴了微电子对应的 内容。特别是最近几年,硅光子单芯 片集成也像集成电路领域经典的摩

收稿日期:2017-08-04 网络出版日期:2017-09-08

基金项目: 国家自然科学基金 (61475144);科技部国际合作项目 (2015DFE12910);安徽省科技攻关计划 项目(1604a0902123)

#### 中图分类号:TN929.5 文献标志码:A 文章编号:1009-6868 (2017) 05-0007-004

摘要: 针对硅光子器件的特殊性提出了与互补金属氧化物半导体(CMOS)工艺兼 容的硅光工艺开发的基本原则和关键问题。相比于工艺,硅光在芯片设计的方法和 流程方面面临更多的挑战,例如硅光子技术与CMOS工艺兼容性,可重复IP制定及 复杂芯片的快速设计等。故充分利用先进的半导体设备和工艺、个别工艺的特殊控 制、多层次光电联合仿真是硅光子芯片从小规模设计走向大规模集成应用的关键。 光子链路的仿真、器件行为级模型、版图的布局布线及验证等是硅光芯片走向成熟 的关键。

Abstract: In this paper, the fundamental principles and key issues of the silicon optical process compatible with complementary metal oxide semiconductor(CMOS) are described. Silicon optics faces many challenges in terms of chip design methods and processes, including the process compatibility of CMOS and silicon photonics, the design of repeatable IP and the quick design of complicate chips. To achieve the change from small scale design to the large scale integrated application, some issues should be emphasized, including the full use of the advanced semi-conductor equipment and process, the control of some special processes and the simulation and design of opto-electronics devices. And the optical link simulation, behavior level model, floor planning, placement and routing, and the layout verification are the key factors to the maturity of silicon optical chip.

Keywords: silicon photonics; design methodology; design flow; large scale integration

尔定律描述的那样,每隔一段时间集 成的器件数量翻番,从而能在相同面 积的芯片上实现更多的功能凹。很多 CMOS晶圆厂及中试平台不断采用更 先进的工艺进行硅光芯片及硅光芯 片与电芯片的集成研究[2-3],这为硅光 芯片打开了大规模集成应用的大 门。硅光芯片的设计者能比较便利 地享受晶圆厂成熟工艺的流片服务, 这是硅光芯片能实现广泛商业化的 前提之一。另外一个前提是:类比集 成电路领域,需要有一套固化的设计 流程,以得到更加完善的电子设计自 动化(EDA)工具的支持和基于单元

器件库的设计方法。

#### 1 硅光工艺的开发

#### 1.1 硅光子的特殊性

硅光子和微电子都是基于硅材 料的半导体工艺,因此将集成光子工 业基于微电子工业之上,使用硅晶作 为集成光学的制造平台将是硅光子 工艺平台的最佳选择。这将使全球 历时50年、投入数千亿美元打造的 微电子芯片制造基础设施可以顺利 地进入集成光器件市场,将成熟、发 达的半导体集成电路工艺应用到集

2017年10月 第23卷第5期 Oct. 2017 Vol.23 No.5 / **07** 中兴通讯技术

成光器件上来,集成光学的工业水平 会得到极大提高,这正是目前发展良 好的硅光子技术的发展思路。

然而,硅光子相对于微电子工艺 有其特殊性,不作修改的微电子工艺 平台无法制备出高性能的硅光子器 件。因此 CMOS 只能提供硅基光电子 加工设备,具体的工艺制备流程仍需 开发。相对于微电子工艺,硅光子特 殊性主要表现在以下几个方面:

- (1)总体路径。硅光子当前的发 展水平相当于20世纪80年代初微电 子的水平,自动化、系统化和规模化 都远远不够。硅光子的发展也不是 像微电子一样延续尺寸和节点减小 的发展路径。目前硅光子的特征尺 寸约为500 nm,最小尺寸在100 nm 左 右,相对于微电子大得多,更小的工 艺节点对硅光子器件本身没有像集 成电路等比缩小这样有特别大的意 义, 当然更小工艺节点的半导体设备 对工艺控制得更好,能在一致性、重 复性和成品率等方面体现优势。

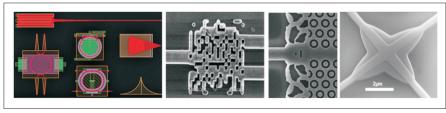

- (2)版图特点。硅光子器件尺寸 差别大,尤其存在许多不规则结构, 如图1所示,这在微电子版图里是基 本没有的。另一方面, 硅光子器件的 特征尺寸(~500 nm)并不是最小尺寸 (~100 nm),这和集成电路是不同 的。工艺过程中往往既需要对最小 尺寸进行控制,又更需要对特征尺寸 进行控制,也对工艺监测和优化提出 了更高的要求。

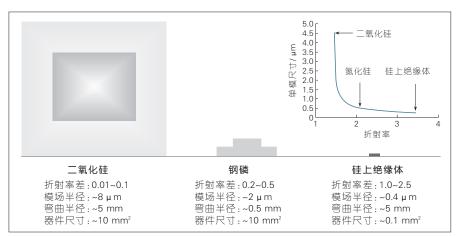

- (3)工艺特殊性。硅光子材料相 对于可编程逻辑控制器(PLC)和铟 磷(InP)等材料体系具有更大的折射 率差,因此波导尺寸可以非常小,如 图2所示。

然而,其带来的缺点是硅光子器 件对尺寸和工艺误差非常敏感,1 nm 的工艺误差足以对硅光子器件性能 带来明显的影响,因此硅光子工艺需 要严格的尺寸精度控制。除了尺寸 精度控制,硅光子器件侧壁粗糙度也 对波导损耗带来巨大影响,必须对制 备工艺进行优化。理论和实验数据 表明:2 nm 的侧壁粗糙度将可以带来 2~3 dB/cm 的波导传输损耗<sup>国</sup>。

(4)材料特殊性。从光电子材料 本身的特性来看,硅材料并不是最好 的选择。由于不是直接间隙半导体 材料,硅基发光一直是一个巨大的难 题。硅没有一阶线性电光效应,因此 也不是最佳的调制器材料。而且,硅 对 1.1 µm 以上波长透明,无法作为通 信波段光探测器材料。为了实现硅 基器件性能的突破,以硅材料为基底 引入多材料是硅光子的必然选择。 如硅基引入 Ge 材料制作 GeSi 探测器 已成为一项标准工艺,需要解决外延 生长过程中大的晶格失配, Kimerling 教授研究小组通过高低温两步生长 工艺较好地解决了该问题。

# 1.2 基于CMOS的硅光子工艺的开发

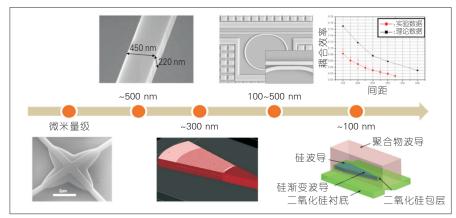

硅光子典型器件如图 3 所示。

硅光子器件尺寸跨度从几十微 米到约100 nm,特征波导的尺寸为 500 nm 左右, 合适的工艺节点大概为 0.13 μm及以下。比利时 IMEC、新加 坡 IME、美国 AIM Photonics 都是采用 200 mm、0.13 μm 来加工硅基光电子 器件。

微电子工艺已经有超过50年的 发展和积累,基于标准CMOS工艺开 发硅光子工艺将是一种最优选和最 经济的方法。在工艺开发过程中需 遵循以下基本原则:

- (1)温度预算。新增或修改的工 艺温度一定要符合整个工艺流程, 如:超过400℃的工艺不能放在后端

- (2)污染控制。可能引入交叉污 染的工艺必须放在污染敏感的工艺

- (3)关键工艺。保证关键工艺性 能,如:最关键的硅波导光刻工艺尽 量在平整表面进行。

- (4)减少修改。尽量减少对标准 CMOS工艺的修改也是工艺流程优化 需要考虑的一个重要方面。

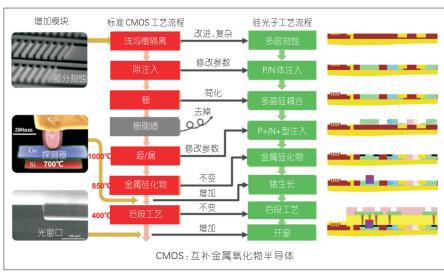

图 4 显示了从标准 CMOS 工艺到 硅光子工艺流程的过程,至少需要对 标准 CMOS 工艺增加 3 个工艺模块: 部分刻蚀、Ge外延生长和光窗成型, 同时需要针对硅光子器件进行大量

▲图1 硅光子不规则版图结构示例

▲图2 PLC、InP、SOI波导折射率差和尺寸对比

中兴通讯技术 08 2017年10月 第23卷第5期 Oct. 2017 Vol.23 No.5

▲图3 硅光子器件典型尺寸

▲图4 基于标准 CMOS 工艺的硅光子工艺流程开发

的工艺参数优化设计,如:第6步的 硅掺杂对调制器的设计非常关键,掺 杂浓度、形貌需要针对硅光子器件进 行优化。

### 2 硅光芯片设计流程及挑战

硅基光电子作为基于 CMOS 工艺 的新兴方向,直接受益于微电子行业 几十年发展的积淀。CMOS平台所能 提供的强大工艺能力,使大规模集成 硅光子器件成为可能[6-7],这是其他光 子集成方向所无法比拟的。如何利 用现有成熟工艺,也是硅基光电子设 计工程师所面临的巨大挑战。目前, 硅光子的设计方法和设计工具,多效 仿或来自于微电子领域的电子设计 自动化(EDA)。EDA对系统功能的 实现多通过已验证元件的组合,这些 元件一般包含于工艺厂提供的工艺 设计包(PDK)。目前在一些硅光子 多项目晶圆(MPW)流片中,工艺厂 已经开始提供PDK用于硅光子领域 的设计四,但是功能仍十分有限。另 一方面, 硅光子设计有其独特的需 求,EDA工具无法满足其自动化设计 需求,亟需针对硅光子设计的硅光子 设计自动化(PDA)工具<sup>[8]</sup>。

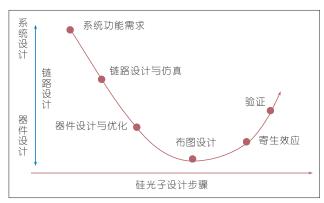

图 5 展示了现阶段的硅光子设计 流程<sup>6</sup>,类似于EDA的流程,硅光子 设计也是从系统功能需求出发。基 于功能分析和分解,设计出光子链 路,并仿真获得其可实现的功能性参 数;进一步地,通过物理仿真与优化, 获得组成光子链路的器件结构及布 图设计:然后基于器件的物理模型, 分析链路集成中的寄生效应并验证 链路功能性,修正设计其结构参数。

在整个硅光子设计流程中,目前 仍面临着诸多挑战。光子链路的仿 真便是其中之一。相比于其他的光 子仿真工具,链路的仿真工具出现较 晚門,仿真方法一般是利用散射矩阵 的形式来描述链路中光子器件及其 之间的连接;但是由于光子器件本身 的结构复杂性,很难使用单一的散射 矩阵来描述其属性。另一方面,现在 的工艺已经可以实现单片数以千计 的无源有源器件混合集成,相互之间 带来的寄生效应更难以用单一矩阵 形式描述,更不用说光电集成时的所 面临的光电混合仿真。

要实现准确的光子链路仿真,其 根本在于构建精确的基础光子器件 的行为模型,这也是硅基光电子设计 目前面临的另一个挑战。在硅基光 电子发展的前10年里,大量的工作 集中于光子器件的物理仿真,以构建 用于光子链路的器件模型;但是受制 于光子器件模型的复杂性,以及其功 能特性对模型结构精确度的敏感性, 很难从物理模型中提取器件的行为 模型,这也导致了光子链路仿真的不 确定性,使得设计流程经常需要在链 路仿真与器件优化之间做更多次的 设计迭代。另一方面,大多数的硅基 光电子器件均是波长依赖型的,并且 严重依赖于材料的温度特性及其他 物理效应,这使得器件模型中所描述 的功能特性仅在特定环境条件下才 是可信的,一旦环境条件改变,额外 的仿真与优化就必不可少。当然,进 一步完备器件模型,是解决该问题的 一个方法,另外还可以根据工作条 件,由设计工具自动地完成环境设置 及器件的额外仿真优化,这是设计工 具的一个发展趋势,不过目前仅有少 数工具可以有限地实现该功能[10-11]。

硅光子链路与器件设计完成后 需要生成掩模版图,用于提交给工艺 厂进行制备。布图的生成一般仍独

◀图 5 硅光子设计流程

立于链路设计,而且多沿用 EDA 中使 用的工具。与电路布图多是横平竖 直的矩形结构不同,硅光子链路及器 件的结构需要考虑导波的需求,尤其 在转弯连接处大多需要采用曲线构 型,从而使硅光子的布图更加复杂。 另外,由于硅光子波导的制备一般仅 使用一层硅材料,这样复杂结构的波 导就需要采用不同深度的刻蚀工艺 来实现,考虑波导器件性能对结构尺 寸的敏感性,实际制备时需要非常精 准的套刻工艺。而对于单次刻蚀工 艺来讲,由于硅光子器件的复杂结 构,在同一掩模中,会出现尺寸跨度 较大的不同结构,使得单步工艺中需 要兼顾各异的刻蚀结构,这几乎是不 可能通过工艺调整来实现的,只能利 用布图的优化与修正来实现。

布图中另一个难点是布局与布 线(P&R)。对硅光子器件来讲,要面 临比电子器件布局中更多的限制,比 如转弯半径、波导间距等,以避免不 必要的损耗和耦合。而器件的连接 则要考虑器件端口结构与连接波导 类型、角度的匹配,对于相位敏感的 链路结构,还需要精确控制不同链路 中的连接波导长度。

在送交布图到工艺厂加工之前, 验证工作也是必不可少的。目前用 于硅光子的验证工具多直接来源于 EDA工具的定制,仅能实现设计规则 检查(DRC)。由于光电器件之间的 诸多差异, DRC 的实现也是十分有限 的,例如版图中常出现的曲线结构, 现有的DRC工具几乎无能为力。另

一项更大的挑战来自于版图和电路 图的对比验证(LVS),由于从硅光子 版图中提取链路模型非常困难,目前 仍没有专门的工具来实现。不过,将 硅光子设计流程集成于统一的开发 环境,是实现该功能的可行涂径。

## 3 结束语

硅光子集成的工艺开发路线和 目标比较明确,困难之处在于如何做 到与CMOS工艺的最大限度的兼容, 从而充分利用先进的半导体设备和 工艺,同时需要关注个别工艺的特殊 控制。硅光子芯片的设计目前还未 形成有效的系统性的方法,设计流程 没有固化,辅助设计工具不完善,但 基于PDK标准器件库的设计方法正 在逐步形成。如何进行多层次光电 联合仿真,如何与集成电路设计一样 基于可重复IP进行复杂芯片的快速 设计等问题是硅光子芯片从小规模 设计走向大规模集成应用的关键。

### 参考文献

- [1] HECHT J. Silicon Photonics Evolve to Meet Real-World Requirements [J]. Laser Focus World, 2013, 49(7):51-53

- [2] LIM A E J, SONG J. Review of Silicon Photonics Foundry Efforts [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2014, 20(4): 405-416. DOI: 10.1109/ JSTOF.2013.2293274

- [3] POLSTER R, THONNART Y. Efficiency Optimization of Silicon Photonic Links in 65nm CMOS and 28-nm FDSOI Technology Nodes [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24 (12): 3450-3459. DOI: 10.1109/ TVLSI.2016.2553673

- [4] BAUDOT C, SZELAG B. Progresses in 300mm DUV Photolithography for the

- Development of Advanced Silicon Photonic Devices[C]//Proceeding of 2015 SPIE Advanced Lithography. USA: SPIE, 2015: 94260D-94262D. DOI:10.1117/12.2085800

- [5] LUAN H C, LIM D R. High-Quality Ge Epilavers on Si with Low Threading-Dislocation Densities [J]. Applied physics letters, 1999, 75(19): 2909-2911

- [6] SOREF R. The Past Present and Future of Silicon Photonics [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2006, 12(6):1678-1687. DOI: 10.1109/ JSTQE.2006.883151

- [7] MUNOZ P. Evolution of Fabless Generic Photonic Integration[C]// Transparent Optical Networks (ICTON), 2013 15th International Conference on, USA:IEEE, 2013; 1-3, DOI: 10.1109/ICTON.2013.6602975

- [8] BOGAERTS W, FIERS M. Design Challenges in Silicon Photonics [J]. IEEE Journal of Selected Topics in Quantum Electronics, 2014, 20(4): 1-8. DOI: 10.1109/ JSTQE.2013.2295882

- [9] FIERS M, VAN V T. Time-Domain and Frequency-Domain Modeling of Nonlinear Optical Components at the Circuit-Level Using a Node-Based Approach[J]. JOSA B, 2012. 29(5): 896-900

- [10] FIER M, LAMBERT E. Improving the Design Cycle for Nanophotonic Components[J]. Journal of Computational Science, 2013, 4 (5): 313-324.DOI: 10.1016/j. jocs.2013.05.008

- [11] ARELLANO C, MINGALEEV S. Efficient Design of Photonic Integrated Circuits (PICS) by Combining Device-and Circuit-Level Simulation Tools[J]. SPIE OPTO, 2013: 862711-862712

#### 作者简介

郭进,中国电子科技集团 公司第三十八研究所高级 工程师;主要研究领域为 CMOS丁艺兼容的硅光子 集成技术;先后参加欧盟 第6框架和第7框架下的 光子集成项目,主持和参 加基金项目10余项;已发 表论文10余篇。

冯俊波,中国电子科技集 团公司第三十八研究所高 级工程师;主要研究领域 为硅基光电子器件与集成 技术;作为项目负责人主 持了国家和省部级顶日共 5项;已在知名杂志上发表 论文30余篇,拥有专利10 余项,参与合著《硅基光电

曹国威,中国电子科技集 团公司第三十八研究所高 级工程师;主要研究方向 为硅光器件自动化设计, 日前主要负责硅光平台 PDK的开发,以及多项目 晶圆流片业务技术支持。

中兴通讯技术 10 2017年10月 第23卷第5期 Oct. 2017 Vol.23 No.5